GIỚI THIỆU CHUNG

FPGA là một loại mạch tích hợp cỡ lớn được cấu thành từ ma trận của các phần tử logic có khả năng tái cấu hình (Configurable Logic Blocks - CLB) và có thể được nối với nhau thông qua các đường kết nối cấu hình (programmable interconnects). Tuy không đạt được mức độ tối ưu như một số ASIC đặc chế hoàn toàn, FPGA lại có một đặc điểm vượt trội là khả năng tái cấu trúc ngay cả khi đang hoạt động [1]. Tính năng tái cấu trúc đơn giản, khả năng thực hiện linh hoạt các thuật toán và tính toán song song với khối lượng lớn các cổng logic, điều này làm cho FPGA có ưu thế vượt trội hơn so với các bộ vi xử lý tuần tự trước nó trong việc giải quyết các bài toán phức tạp đòi hỏi khối lượng tính toán lớn và các hệ thống thời gian thực. Cấu trúc đặc thù của FPGA cũng mang lại hiệu quả đặc biệt trong việc thực thi các thuật toán mật mã, đặc biệt là các thuật toán mã khối.

Ngoài khả năng tái cấu trúc vi mạch toàn cục, một số FPGA hiện đại còn hỗ trợ tái cấu trúc cục bộ, tức là khả năng tái cấu trúc từng bộ phận riêng lẻ (partial configuration) trong khi vẫn đảm bảo hoạt động bình thường cho các bộ phận khác. Đây là chức năng cho phép ứng dụng có thể tái cấu trúc một phần thiết kế theo yêu cầu mà không cần phải dừng hay ngừng hệ thống để lập trình lại toàn bộ. Tái cấu trúc từng phần động (Dynamic Partial Reconfiguration - DPR) có thể được khai thác trong nhiều lĩnh vực ứng dụng như để đáp ứng các yêu cầu về không gian trong các hệ thống di động nhỏ, tạo ra một hệ thống trên chip với mức độ linh hoạt cao, hoặc thực hiện các thuật toán phần cứng thích ứng,... [2] Các hãng đã hỗ trợ tính năng này bắt đầu từ Virtex 4 (Xilinx) và Strarix 5 (Altera) trong các bộ phần mềm thiết kế EDA của họ (ISE và Quartus).

HỆ THỐNG TÁI CẤU TRÚC TỪNG PHẦN ĐỘNG TRÊN FPGA

Tái cấu trúc từng phần động cho phép FPGA thích ứng với việc thay đổi thuật toán phần cứng, cải thiện khả năng chịu lỗi và sử dụng tài nguyên, nâng cao hiệu suất hoặc giảm mức tiêu thụ điện năng [3]. DPR đặc biệt có giá trị khi các thiết bị hoạt động trong môi trường quan trọng không thể bị gián đoạn trong khi một số hệ thống mô-đun cần được xác định lại. Có 2 phương pháp cấu hình lại một phần động được đề xuất, bao gồm cấu hình lại một phần dựa trên sự khác biệt và cấu hình lại một phần dựa trên mô-đun [4].

Tái cấu trúc từng phần dựa trên sự khác biệt: Được sử dụng khi một thay đổi nhỏ được thực hiện đối với thiết kế và đặc biệt hữu ích trong trường hợp thay đổi các phương trình trong Bảng tra cứu (LUT) hoặc nội dung khối bộ nhớ chuyên dụng. Dòng bit phần thiết kế mới chỉ chứa thông tin về sự khác biệt giữa cấu trúc thiết kế hiện tại (nằm trong FPGA) và nội dung thiết kế mới. Chuyển đổi cấu hình của một mô-đun từ triển khai này sang triển khai khác rất nhanh chóng do sự khác biệt giữa dòng bit có thể cực kỳ nhỏ so với toàn bộ dòng bit của thiết bị [4].

Tái cấu trúc từng phần dựa trên mô-đun: Sử dụng các khái niệm thiết kế mô-đun để cấu hình lại các khối logic lớn. Trong tái cấu từng phần dựa trên mô-đun, phần cứng của FPGA được thiết kế thành từng mô-đun cấu hình lại được RM (Reconfigurable Module), sau đó tổng hợp vào hệ thống. Phần tĩnh được đặt trong khu vực “tĩnh” của FPGA và không thay đổi trong suốt quá trình hoạt động của hệ thống. Phần này chịu trách nhiệm điều khiển quá trình hoạt động của toàn hệ thống trong thời gian chạy ứng dụng và điều khiển quá trình tái cấu trúc cho các mô-đun [4].

THỰC THI TÁI CẤU TRÚC TỪNG PHẦN ĐỘNG TRÊN FPGA

Trong thiết kế của nhóm tác giả, phần tĩnh bao gồm các khối sau: Một vi xử lý nhúng Microblaze đóng vai trò xử lý trung tâm và điều khiển các hoạt động cấu hình lại của hệ thống thông qua Bus AXI/PLB. Khối UART thực hiện chức năng kết nối với máy tính để truyền nhận dữ liệu, tín hiệu điều khiển người dùng và hiển thị kết quả. Bộ định thời (timer) xác định thời gian cấu hình của hệ thống.

Khối HWICAP (Hardware-Internal Configuration Access Port) là một lõi cứng được cung cấp bởi Xilinx với AXI-CAP sử dụng cho Bus AXI; nó đóng vai trò rất quan trọng trong hệ thống tái cấu hình động với chức năng nhận tệp cấu hình từ bộ nhớ ngoài để nạp xuống khu vực cấu hình động trên FPGA [5]. Phần động (phần cấu hình lại được) là các mô-đun chức năng trong hệ thống có thể thay thế, sửa đổi hoặc gỡ bỏ ngay trong thời gian hệ thống đang chạy để thích nghi với yêu cầu cấu trúc của hệ thống thực hiện trên FPGA. Người dùng xác định chức năng cần sử dụng thông qua chương trình điều khiển. Các mô-đun động được tái cấu trúc bằng cách sử dụng cổng truy cập cấu hình bên trong - ICAP (Internal Configuration Access Port) có sẵn thông qua lõi AXI HWICAP.

Sau khi phần cứng của hệ thống được thiết lập, chương trình điều khiển sẽ giám sát quá trình cấu hình cũng như đo đạc một vài thông số thời gian hay tốc độ cấu hình.

Cấu hình phần cứng FPGA

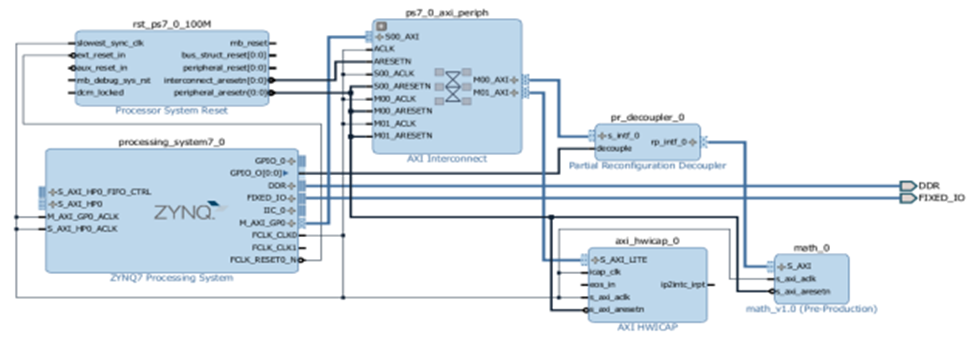

Hệ thống tái cấu trúc từng phần được xây dựng trên nền tảng công cụ phần mềm Vivado 2016.3 với board thử nghiệm là Z-turn Zynq-7020 (XC7Z020) của Xilinx. Hệ thống bao gồm các lõi IP core được kết nối như trên Hình 1.

Các thành phần của hệ thống tái cấu hình từng phần bao gồm:

- Processing_systerm7_0: Lõi vi xử lý nhúng Microblaze có chức năng điều khiển toàn bộ hoạt động của hệ thống theo chương trình ứng dụng mà người dùng mong muốn.

Hình 1. Hệ thống tái cấu trúc từng phần được thực thi trên FPGA

- Rst_ps7_0_100M: Khối tạo tín hiệu Clock và Reset, cấp xung Clock cho toàn bộ hệ thống phù hợp với nhu cầu người dùng (tần số hoạt động là 100MHz). Đồng thời tạo ra tín hiệu Reset kết nối đồng bộ với chân điều khiển reset hệ thống trên Board phát triển.

- Ps7_0_axi_periph: Thực hiện kết nối các IP core trong hệ thống sử dụng bus AXI. Thông thường, các IP ngoại vi của Xilinx sẽ được điều khiển và cấu hình thông qua bus AXI này.

- Axi_hwicap_0: ICAP được xây dựng dựa trên phần cứng (Hardware ICAP), là thành phần cốt lõi của hệ thống cấu hình lại một phần động dựa trên SRAM của Xilinx. Nó cho phép bộ vi xử lý nhúng MicroBlaze đọc và ghi bộ nhớ cấu hình FPGA. Điều này cho phép người dùng viết các chương trình phần mềm có thể sửa đổi cấu trúc và chức năng mạch FPGA trong quá trình vận hành hệ thống.

- Math_0: Phân vùng tài nguyên được sử dụng để thực hiện các mô-đun tái cấu trúc từng phần, chính là vùng cấu trúc của thiết kế chính cho hệ thống làm việc. Trong thiết kế minh họa của nhóm tác giả, các mô-đun tái cấu hình được sử dụng với mục đích kiểm tra thiết kế hệ thống là bộ cộng và bộ nhân.

Hoạt động của hệ thống cũng tương tự như các hệ thống nhúng khác, vi xử lý sẽ quản lý và điều khiển các ngoại vi thông qua không gian địa chỉ đã được định ra khi cấu hình.

Chương trình điều khiển

Một chương trình phần mềm được xây dựng để điều khiển hoạt động của hệ thống. Trong đó, người dùng xác định các phân vùng bộ nhớ của hệ thống được định ra khi cấu hình, kiểm soát các tệp dữ liệu đưa vào hệ thống và đưa tín hiệu điều khiển để lựa chọn mô-đun cấu hình lên vùng tái cấu hình đã định.

Chương trình điều khiển thực hiện một số nhiệm vụ cơ bản như sau:

- Khởi tạo quy định địa chỉ và độ lớn của tệp bitstream cho các mô-đun tái cấu trúc.

- Kiểm tra tính hợp lệ của các tệp dữ liệu đầu vào.

- Truyền tham số lựa chọn module tái cấu trúc.

Thử nghiệm hoạt động của hệ thống

Theo kịch bản thử nghiệm, với thiết kế chính là các bộ toán học, có 2 mô-đun tái cấu trúc có thể lựa chọn là bộ cộng và bộ nhân tùy theo giá trị của biến khởi tạo được nhập vào. Giá trị khởi tạo là 1 tương ứng với việc tái cấu trúc cho mô-đun bộ nhân, là 2 tương ứng với mô-đun bộ cộng, là 3 sẽ không cấu hình mô-đun nào (mô-đun Blank). Người dùng sau khi lựa chọn mô-đun tái cấu trúc mong muốn có thể nhập các giá trị tính toán để thử nghiệm hoạt động của hệ thống. Với bộ cộng và bộ nhân, tính toán các tham số cho kết quả đúng như mong đợi. Với mô-đun Blank, vì không cài đặt thuật toán nên sẽ không đưa ra kết quả tính toán đúng.

.png)

Hình 2. Kết quả thử nghiệm khi cấu hình bộ cộng

Hình 2 là kết quả tính toán thử nghiệm với mô-đun cộng. Kết quả cho thấy hệ thống tái cấu trúc từng phần đã hoạt động ổn định, đáng tin cậy. FPGA với khả năng tái cấu túc từng phần sẽ cho phép xây dựng các hệ thống có hiệu suất cao, cho phép thực hiện nhiều nhiệm vụ mà không cần phải xây dựng lại phần cứng và khả năng thay đổi phần cứng linh hoạt ngay cả khi thiết bị đang hoạt động, giảm thời gian cấu hình lại hệ thống. Chúng trở thành nền tảng phần cứng quan trọng, đáp ứng các mục tiêu về độ tin cậy và hiệu suất mà một hệ thống yêu cầu.

ỨNG DỤNG TÁI CẤU TRÚC TỪNG PHẦN CHO BÀI TOÁN AN TOÀN THIẾT KẾ FPGA

Lợi thế quyết định của FPGA khi so sánh với vi mạch phần cứng thông thường là khả năng tái cấu hình linh hoạt. Người dùng tải bitstream thiết kế từ bộ nhớ bên ngoài để cấu hình lên thiết bị. Do vậy, sẽ có nhiều nguy cơ bảo mật liên quan đến sao chép trái phép bitstream thiết kế này nhằm nhân bản và dịch ngược thiết kế. Điều này mang đến những mối đe dọa đối với tài sản trí tuệ của nhà thiết kế, lợi ích kinh tế của doanh nghiệp và thậm chí là an ninh quốc gia.

.png)

Hình 3. Mô hình giải pháp bảo mật bitstream cấu hình của FPGA

.png)

Một trong những giải pháp hữu hiệu để bảo mật bitstream thiết kế cho FPGA là sử dụng thuật toán mật mã. Giải pháp được thực hiện kết hợp giữa phần mềm trên máy tính và phần cứng cấu hình trên FPGA. Mô hình thực hiện giải pháp được mô tả khái quát như trên Hình 3.

Tệp bitstream của thiết kế chính cần bảo vệ (các mô-đun tái cấu trúc từng phần: bộ cộng và bộ nhân) được mã hóa với thuật toán GOST 28147-89 nhờ chương trình phần mềm trên máy tính. Hệ thống tái cấu trúc từng phần bao gồm lõi IP giải mã được xây dựng và tạo tệp bitstream để cấu hình phần cứng lên FPGA.

Một chương trình phần mềm sẽ điều khiển luồng thông tin và hoạt động của hệ thống tái cấu trúc. Bitstream thiết kế sau khi được giải mã sẽ được ghi lên phần IP tái cấu trúc đã định sẵn trên FPGA để thực hiện chức năng chính của hệ thống. Như vậy, tệp bitstream thiết kế hệ thống chính đã được bảo vệ bằng thuật toán mật mã và được giữ an toàn cho đến khi ghi xuống FPGA.

Hệ thống tái cấu trúc từng phần được xây dựng thử nghiệm trên board Z-turn bao gồm các lõi IP core được kết nối như trên Hình 4.

KẾT LUẬN

Bài báo đã giới thiệu một cách khái quát về một hệ thống tái cấu trúc từng phần trên FPGA với những lợi ích thiết thực mà nó mang đến. Nhóm tác giả đã thử nghiệm thành công một hệ thống tái cấu trúc từng phần trên board phát triển Z-turn Zynq-7020. Kết quả cho thấy hệ thống hoạt động ổn định, đáng tin cậy, các mô-đun tái cấu trúc từng phần hoạt động đúng chức năng như mong đợi. Từ đó, nhóm tác giả đã định hướng xây dựng một giải pháp an toàn cho tệp bitstream thiết kế của FPGA sử dụng chính hệ thống tái cấu trúc từng phần này.

TS. Nguyễn Chung Tiến, Trần Bình Nhung (Học viện Kỹ thuật mật mã)